JFE-TEC News

No.20「極低加速電圧SEMによるトランジスタのpn接合観察」

JFE-TEC News No.20号 極低加速電圧SEMによるトランジスタのpn接合観察 他 記事一覧

極低加速電圧SEMによるトランジスタのpn接合観察

全文 PDF (430.7 KB)

No.20 極低加速電圧SEMによるトランジスタのpn接合観察 他

極低加速電圧SEMによるトランジスタのpn接合観察

極低加速電圧走査顕微鏡(ULV-SEM:Ultra Low accelerating Voltage Scanning Electron Microscope)は、最小100Vまで加速電圧を低くすることで、ナノメータレベルの極表面観察、絶縁物の導電処理無しでの観察、20nmレベルの高分解能EDX分析などが可能という特徴があります。これらに加えて、ULV-SEMでは、従来のSEMで捉えられなかった物質状態の違いを、明るさの異なる像として観察することができます。今回この特徴を応用し、半導体トランジスタのpn接合状態の観察に成功しました。

トランジスタのpn接合観察

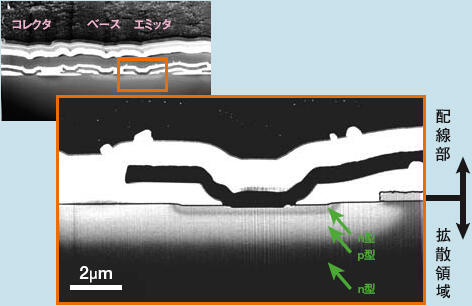

p型とn型の半導体が接してできるpn接合は半導体デバイスの基本構造です。しかし、実際どのようなpn接合が形成されているのかを直接確認する方法は限られていました。当社では、物質状態の違いを捉えられるULV-SEMでこのpn接合を観察しました。写真の電子デバイスはバイポーラトランジタと呼ばれるもので、p型拡散領域を形成したのち、それよりも高濃度のn型ドーパントを拡散してpn接合が形成されています。このエミッタ部に形成されているpn接合界面が、p型領域が明るく、n型領域が暗いコントラストとして観察されました。この SEM像により、それぞれの領域の形や大きさ、pn接合界面の位置などが設計どおりにできているか分かります。また、不良が生じた際に、pn接合の形成の問題であるか確認ができます。

今後の電子デバイスへの応用

このようにpn接合状態が観察できたことで、電子デバイスへのULV-SEMの応用範囲はさらに広がったといえます。現在、半導体デバイスの主流を占めているMOS型トランジスタや、その他電子デバイスの分析評価への応用も始めています。当社では、ULV-SEMなど、材料の状態の違いを可視化する解析技術を通して、今後とも、電子デバイスをはじめとする各種材料のR&Dやトラブルシューティングに関する幅広いニーズに応えてまいります。

写真 バイポーラ型トランジスタのエミッタ断面のpn接合部のULV-SEM観察

関連リンク・関連記事

このページに関する

お問い合わせはこちらから

- JFEテクノリサーチ株式会社 営業本部

- 0120-643-777